# **+**IJESRT

## INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

## OPTIMIZED SYSTEM LEVEL DESIGN AND SIMULATION ANALYSIS FOR CHARACTERIZATION OF PERFORMANCE OF SINGLE-LOOP CT SIGMA-DELTA MODULATORS A/D

Anil Kumar Sahu <sup>\*1</sup>, Vivek Kumar Chandra <sup>2</sup>, G R Sinha<sup>3</sup>

\* Assistant Professor (ETC) ,Shri Shankaracharaya Technical Campus (SSTC) Bhilai, India Professor and Head (EEE), Chhatrapati Shivaji Institute of Technology Durg India Professor (ETC) and Dean, CMR Technical Campus Hyderabad India

DOI: 10.5281/zenodo.886907

## ABSTRACT

This paper demonstrates a possibility to realize a simulation of testing strategy of high-resolution Sigma-Delta modulator using MATLAB SIMULINK and Xilinx EDA tool environment. This brief works explore towards smart computation static and dynamic parameter of sigma delta Analog and converter (ADC) .Novelty of computation method introduce here in the Output Response Analyzer (ORA) and On chip test generation being used for testing of ADC parameters which help in reducing the difficulties in design complexity of integrated circuit . Moreover, the reusable features of hardware in the computation of different parameters are also improved in the ORA design of BIST.

KEYWORDS: Sigma delta modulator, Resolution, Noise Calculation, Power Calculation.

## I. INTRODUCTION

Continuous time sigma delta modulator's are affected by the non ideal behaviour of analog circuit which limits their resolution in MHz bandwidth[1-2]. The non idealities of circuit and quantization noise constitute the modulator's noise floor. The error to be reduced or noise has its own power penalty depending on the Oversampling ratio (OSR), quantizer bit length (Nc), the modulator's noise shaping order (Lc), The share of each error in modulator's noise floor and OSR, Nc, Lc are the most important design parameters which will be responsible for minimizing the power consumption of a bandwidth and resolution[3-7]. To get the optimum loop filter coefficients and the amplifiers specifications are the objective of given system level design approach. The loop filter coefficients are optimized for the minimum quantization noise and the amplifiers specification are optimized for the minimum power consumption[8]. The task of testing a VLSI chip to guarantee its functionality is exceptionally complex and often very time taking. In addition to the difficulty of testing the chips (IC) themselves, the incorporation of the chips into systems has caused test generation's cost to grow highly. On the other hand, in built-in self-test, the test pattern generation and the output response evaluation are done on chip; thus, the use of high-end automatic test equipment (ATE) machines to test chips can be avoided[9-12]. High-resolution ADCs with high sampling rates are required in a broad area of high-performance applications, such as high-grade imaging systems, wireless communications, and radar[9]. To deliver ADCs satisfying the requirements of the applications, it is obligatory that they are tested as less time as possible, but without negotiating the quality of the test[11]. So with reduced size, cost and power consumption, the promotion towards the development of new generation of electronics system accomplishing all major features for the interaction of real time world to the digital processing circuitry is in its great demand[12][13].

A Successful system level modelling of sigma delta BIST for ADC linearity testing must satisfied following Condition: First, it include modelling of TSG Test signal generator and post silicon implementation of TSG so that Low cost and Area overhead is minimize on chip and more accurate stimulus needed than ADC under test. Second System level Modelling and physical design of DUT as analog to digital converter play very important role[14-18]. Analog to digital linearity characteristics is mesuresued by two popular instruments such as INL and DNL. Integral nonlinearity(INL) and differential nonlinearity(DNL) can be calculated accurately from

estimation of ADC's transition levels. The most powerful approach to estimate transition level of ADC's is histogram test which gives solution of full code testing [19-23].

Noise parameter which affects the resolution of continuous time sigma delta modulator are:

- Thermal noise

- Clock jitter noise

- Quantization noise

- Limited gain bandwidth

- Slew rate of amplifiers

The errors which are mentioned above , can be reduced or eliminated by system or circuit level techniques carries a low part of modulator's noise floor (10-20%). The calculations of Thermal noise and clock jitter noise have a more power reductions and they form usually (70-80)% of the modulator's noise floor[5-6]. This shows thermal noise and clock jitter noise mainly affects the modulator's noise floor. On the other hand, quantization noise contains (5-10%) of the modulator's noise floor[7-10].

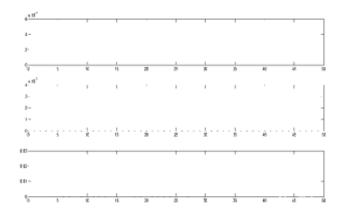

## **II.** Method: (GUI of Power Consumption)

The Power of countinuous time sigma delta modulator is estimated in terms of its system level parameters. we calculate separately the power budget of each modulator.

| Filman     | [Miki]   | NC      | 71        | Kolema     |                 |             |     |

|------------|----------|---------|-----------|------------|-----------------|-------------|-----|

| 93135      | U.       |         | -         | 100        | Parent          | 3 5.750-38  |     |

| <b>EMN</b> | R        | 101     | OSR       | HENRY      | - Wester        |             |     |

| 1.881      | - 3000 E | 1 4.0s. | C.La C.L  | The second | Han             | 0.472985    |     |

| KCR        | 1 St     |         |           |            |                 |             |     |

| BONA-S     | -        |         |           |            | - na            | a one cases |     |

| - 00       | Ginc     | wer     | ILE       |            | Interesting the |             |     |

|            | ((       | 10.00   | a all     |            | -               | 8.0027720   |     |

| T          | BW       | - atta  | NE        | aī         |                 |             |     |

| 214        |          | 2.42    | 1         | (10)       | ine i           | 8.252019    | 760 |

| Y          | Pare     | n (00 m | PO        |            |                 |             |     |

| 1.4.       | 1 Certes | 100     | CERNICA . |            | PERCENT.        | 1 2 10427   |     |

Figure 1. GUI of Power consumption .

Figure 2. Power consumption Vs OSR.

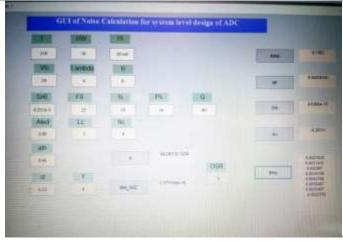

As we have prepared a graphical user interface for the noise calculation presented in the secton II. Foe different values of all the parameters we are getting various values of noise parameters.

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

Figure 3. GUI of Noise Calculation

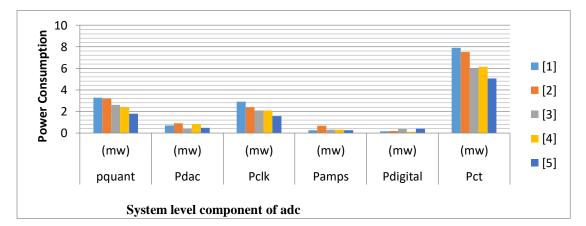

## III. RESULTS AND DISCUSSION

As we have prepared a graphical user interface for the noise calculation presented in the secton II. Foe different values of all the parameters we are getting various values of noise parameters .

| Re<br>f | BW<br>(MHz) | B(bit) | L<br>c | N<br>c | IBN_t<br>h | IBN_NR<br>Z | IBN<br>_q |

|---------|-------------|--------|--------|--------|------------|-------------|-----------|

| [1]     | 18          | 8      | 3      | 4      | 0.113      | 0.24        | 2.7       |

| [2]     | 20          | 8      | 3      | 4      | 0.240      | 0.42        | 3.1       |

| [3]     | 25          | 16     | 3      | 5      | 0.340      | 0.48        | 3.2       |

| [4]     | 36          | 16     | 4      | 1      | 0.140      | 0.36        | 3.4       |

Table 1 Noise Calculation Table

Figure 4. Comparative Noise Calculation

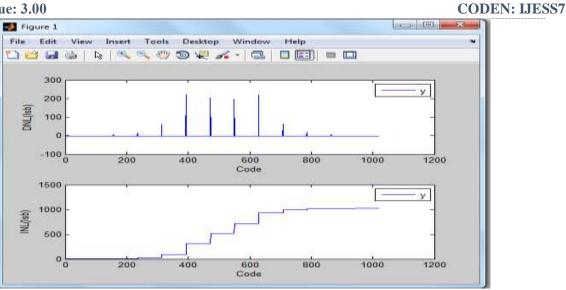

Figure 5. SIMSIDES Computation of INL and DNL

Histogram Calculator: DNL, INL and SNRd is calculated using performing following equation(1),(2),(3).

$$DNL(K^{th}code) = \frac{W_k - 1LSB}{1LSB}$$

$$INL(K^{th}code) = \sum_{i=0}^{i=k-1} \frac{W_i - KLSB}{1LSB}$$

(2)

$$SNR_d = -10\log(Error)$$

(3)

**ISSN: 2277-9655**

**Impact Factor: 4.116**

## **IV.** CONCLUSION

In this paper noise parameters and power consumption in single stage sigma delta modulator are analytically extracted. The power consumption of different possible design of CT sigma delta modulator are compared to choose the best one. GUI allows us to get the power values without actually simulating the circuit design. Further , The transistor level design can be implemented and the author is free to use any tool for the designn. Here selected different values of OSR , Lc , Nc and various parameter and got different values of power and in recent results for Lc=3 , Nc=4 , B= 12 . Therefore, the accuracy of the proposed technology is considerably high. Since the proposed technology is entirely a digital circuit therefore, the performance of the modulator ORA will not be degraded. In addition, the obtained parameters are tested by using BIST technology. This worked us foused our system level Modeling and Post simulation strategy to obtain fast and accurate prototype of the ADC Built –In-self-test of sigma –delta based ADC. Our approach consist of modelling and design of an accurate first order sigma delta modulation based ADC. The synthesis result using a 180 nm library and MATLAB Simulink is used .

#### V. ACKNOWLEDGEMENTS

The authors would like to thanks the management, SSTC SSGI institute for providing MATLAB Simulink and Xilinx EDA tool .

#### VI. REFERENCES

- [1] H.pakniat m.yaveri, system level design and optimization of single loop CT sigma delta modulators for high resolution wideband applications.

- [2] P. Shettigar, S. Pavan, Design techniques for wideband single-bit continuous-time  $\Sigma\Delta$ -modulators with FIR feedback DACs IEEE J. Solid-State Circuits, 47 (12) (2012).

[Sahu\* et al., 6(9): September, 2017]

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

- [3] G. Mitteregger, C. Ebner, S. Mechnig, T. Blon, C. Holuigue, E. Romani. A 20-mW 640-MHz CMOS continuous-time ΣΔ ADC with 20-MHz signal bandwidth, 80-dB dynamicrange and 12-bit ENOB , IEEE J. Solid-State Circuits, 41 (12) (2006).

- [4] T. Brückner, C. Zorn, J. Anders, J. Becker, W. Mathis, M. Ortmanns A GPU-acceleratedweb-based synthesis tool for CT sigma-delta modulators, IEEE Trans. Circuits Syst. I: Regul.Pap., 61 (5) (2014).

- [5] S. Pavan, N. Krishnapura, R. Pandarinathan, P. Sankar A power optimized continuous timeΣΔ ADC for audio applications, IEEE Trans. Circuits Syst. I: Regul. Pap., 43 (2) (2008).

- [6] S.D. Kulchycki, R. Trofin, K. Vleugels, B.A. WooleyA 77-dB dynamic range, 7.5-MHz hybrid continuous-time/discrete-time cascaded ΣΔ modulator, IEEE J. Solid-State Circuits, 43 (4) (2008)

- [7] Sahu, A. K., Chandra, V. K., & Sinha, G. R. (2014). 'Improved SNR and ENOB of Sigma-Delta Modulator for Post Simulation and High Level Modeling of Built-in-Self-TestScheme. International Journal of Computer Applications.

- [8] Abbes, K., A. Hentati, and M. Masmoudi. "Test and characterization of 1 bit Σ—Δ modulator." In Systems, Signals and Devices, 2008. IEEE SSD 2008. 5th International Multi-Conference on, pp. 1-4. IEEE, 2008.

- [9] Lee, Kuen-Jong, Soon-Jyh Chang, and Ruei-Shiuan Tzeng. "A sigma-delta modulation based BIST scheme for A/D converters." In Test Symposium, 2003. ATS 2003. 12th Asian, pp. 124-127. IEEE, 2003.

- [10] Damarla, Raju T., Wei Su, Moon J. Chung, Charles E. Stroud, and Gerald T. Michael. "A built-in self test scheme for VLSI." In Design Automation Conference, 1995. Proceedings of the ASP-DAC'95/CHDL'95/VLSI'95., IFIP International Conference on Hardware Description Languages. IFIP International Conference on Very Large Scal, pp. 217-222. IEEE, 1995.

- [11] Hawrysh, Evan M., and Gordon W. Roberts. "An integration of memory-based analog signal generation into current DFT architectures." In Test Conference, 1996. Proceedings., International, pp. 528-537. IEEE, 1996.

- [12] Huang, Jiun-Lang, Chee-Kian Ong, and Kwang-Ting Cheng. "A BIST scheme for on-chip ADC and DAC testing." In Proceedings of the conference on Design, automation and test in Europe, pp. 216-220. ACM, 2000.

- [13] Xing, Hanqing, Hanjun Jiang, Degang Chen, and Randall L. Geiger. "High-resolution ADC linearity testing using a fully digital-compatible BIST strategy." Instrumentation and Measurement, IEEE Transactions on 58, no. 8 (2009): 2697-2705.

- [14] [Duan, Jingbo, Degang Chen, and Randall Geiger. "Cost effective signal generators for ADC BIST." In Circuits and Systems, 2009. ISCAS 2009. IEEE International Symposium on, pp. 13-16. IEEE, 2009.

- [15] Huang, Jiun-Lang, and Kwang-Ting Cheng. "Testing and characterization of the one-bit first-order delta-sigma modulator for on-chip analog signal analysis." In Test Conference, 2000. Proceedings. International, pp. 1021-1030. IEEE, 2000.

- [16] Wen, Yun-Che, and Kuen-Jong Lee. "An on chip ADC test structure." In Proceedings of the conference on Design, automation and test in Europe, pp. 221-225. ACM, 2000..

- [17] Bandopadyay, T. K., Manish Saxena, and Raghav Shrivastava. "Sigma Delta Modulator with Improved Performance through Evolutionary Algorithm." International Journal of Science and Research (IJSR) Volume 2 Issue 3, March 2013.

- [18] Benabes, Philippe. "Accurate time-domain simulation of continuous-time sigma-delta modulators." Circuits and Systems I: Regular Papers, IEEE Transactions on 56.10 (2009): 2248-2258.

- [19] C. H. E. N. Zhicai, Mathew Bond, and Nijad Anabtawi. "Design of a Second Order Continuous Time Sigma Delta Modulator with Improved Dynamic Range." Final Project of Oversampling Class, Fall 2007 Arizona State University.

- [20] Hart, Adam, and Sorin P. Voinigescu. "A 1 GHz Bandwidth Low-Pass ADC With 20-50 GHz

- [21] Prateek Verma, Anil Kumar Sahu, Dr. Vivek Kumar Chandra, Dr. G.R.Sinha. A Graphical User Interface Implementation of Second Order Sigma- Delta Analog to Digital Converter with Improved Performance Parameters, International Journal For Research In Applied Science And Engineering Technology, Vol. 2 Issue VII, July 2014.

- [22] Anil Kumar Sahu, Vivek Kumar Chandra and Dr. G. R. Sinha "Optimized System Level Modeling of CORDIC Enabled Built-in-Self-Test of Sigma-Delta Analogto-Digital Converter "2017 2nd International Conference for Convergence in Technology (I2CT)" Pune, 7th -9th April-2017, DOI:978-1-5090-4307-1/17/\$31.00 ©2017 IEEE.

## [Sahu\* et al., 6(9): September, 2017]

IC<sup>TM</sup> Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116 CODEN: IJESS7

[23] Anil Kumar Sahu, Vivek Kumar Chandra and Dr. G. R. Sinha "High level Computation Technique for Characterization of Sigma-Delta A/D "The International Conference on Microelectronics Devices, Circuits and Systems (ICMDCS 2017) will be held at the VIT University, Vellore India from 10th to 12th August 2017.

## **CITE AN ARTICLE**

Sahu, A. K., Chandra, V. K., & Sinha, G. R. (2017). OPTIMIZED SYSTEM LEVEL DESIGN AND SIMULATION ANALYSIS FOR CHARACTERIZATION OF PERFORMANCE OF SINGLE-LOOP CT SIGMA-DELTA MODULATORS A/D . *INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY*, 6(9), 249-254. Retrieved September 15, 2017.